2000 © IMP, Inc.

408-432-9100/www.impweb.com

1

IMP1

IMP1

233M

233M

P

OWER

M

ANAGEMENT

Key Features

Applications

N Set-top boxes

N Cellular phones

N PDAs

N Energy management systems

N Embedded control systems

N Printers

N Single board computers

N Improved Dallas DS1233M replacement

-- 60% lower maximum supply current

N Low Supply Current

-- 20µA maximum (5.5V)

-- 15µA maximum (3.6V)

N Automatically restarts a microprocessor after

power failure

N 350ms reset delay after V

CC

returns to an

in-tolerance condition

N Active LOW power-up reset, 5k internal pull-up

N Precision temperature-compensated voltage

reference and comparator

N Eliminates external components

N Pin function compatible with the Motorola

MC33064, MC34064, MC33164 and MC34164

N Motorola 68xxx and HC16 compatible

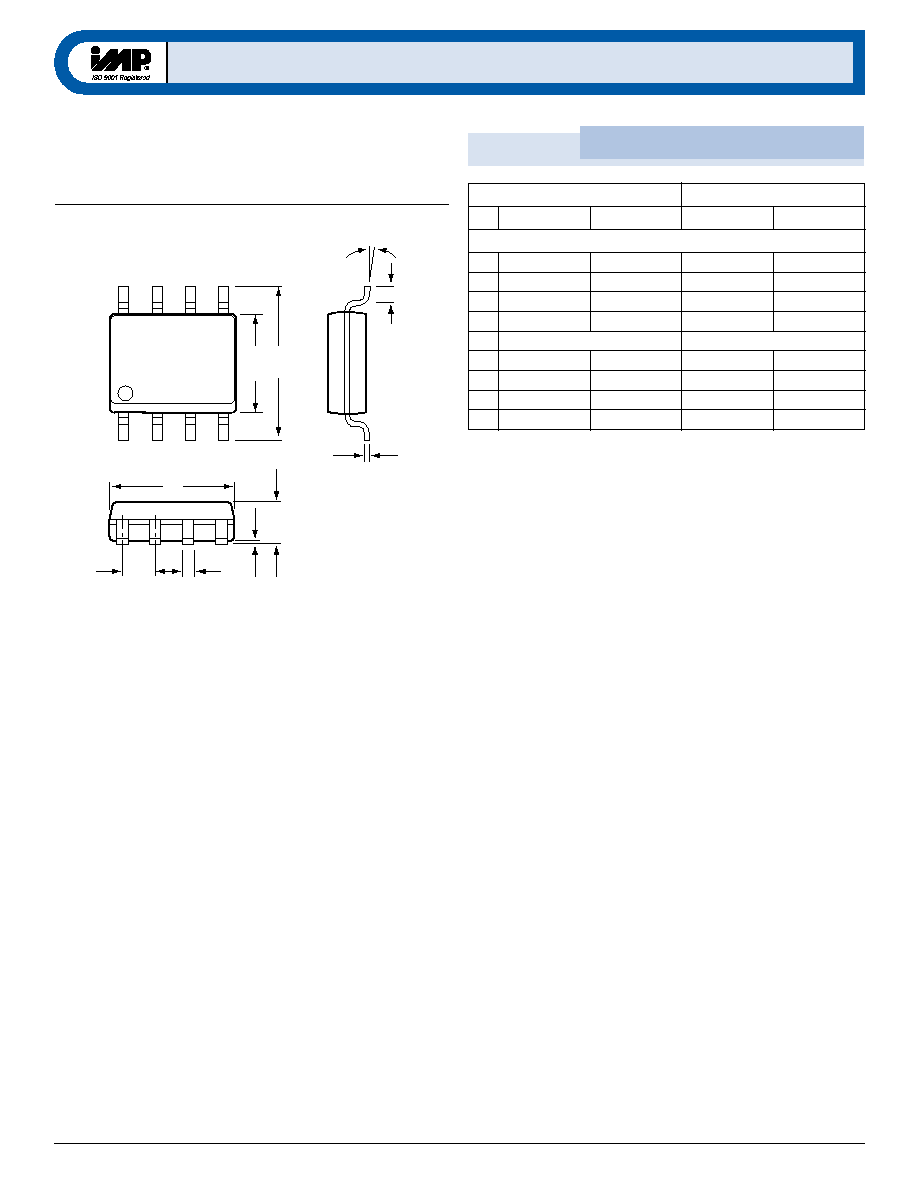

N Compact surface mount SO-8 package

N Operating temperature ≠40∞C to +85∞C

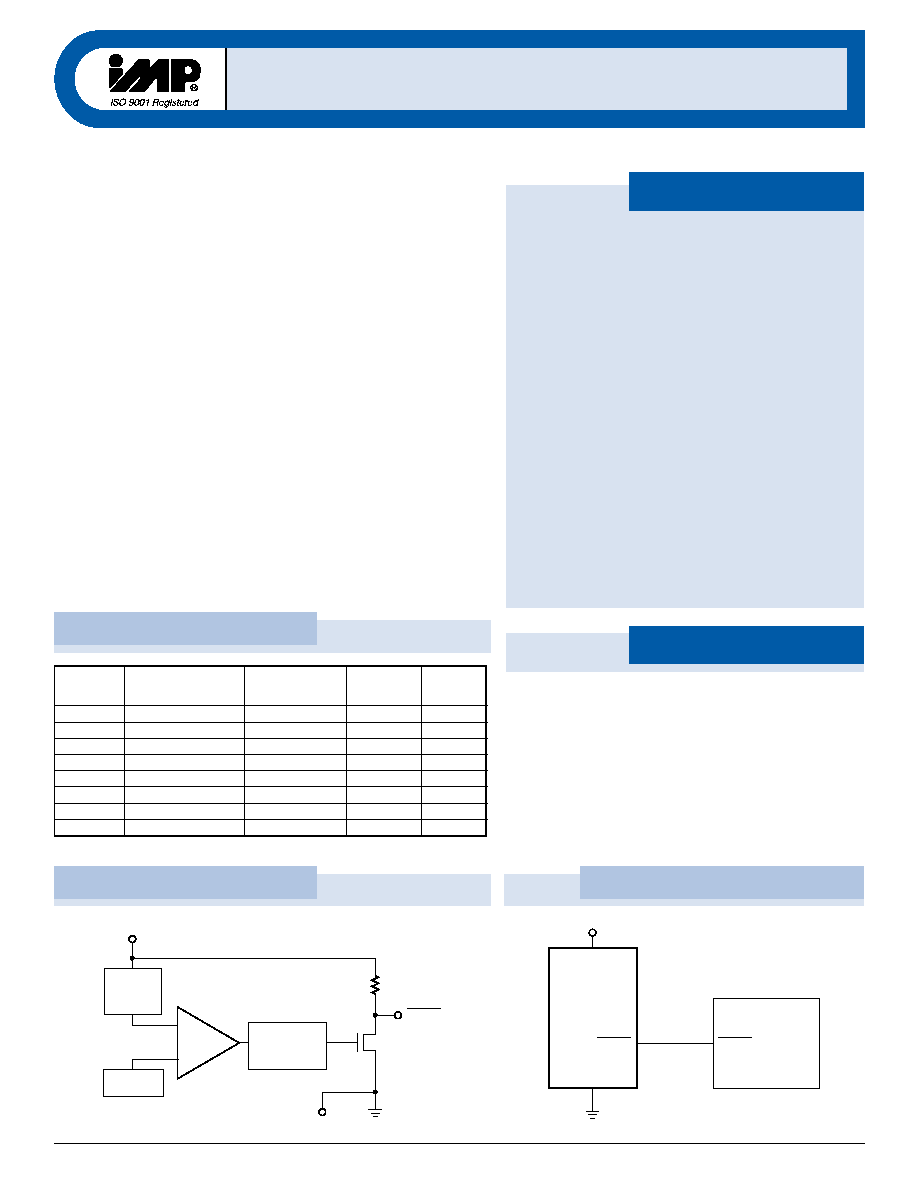

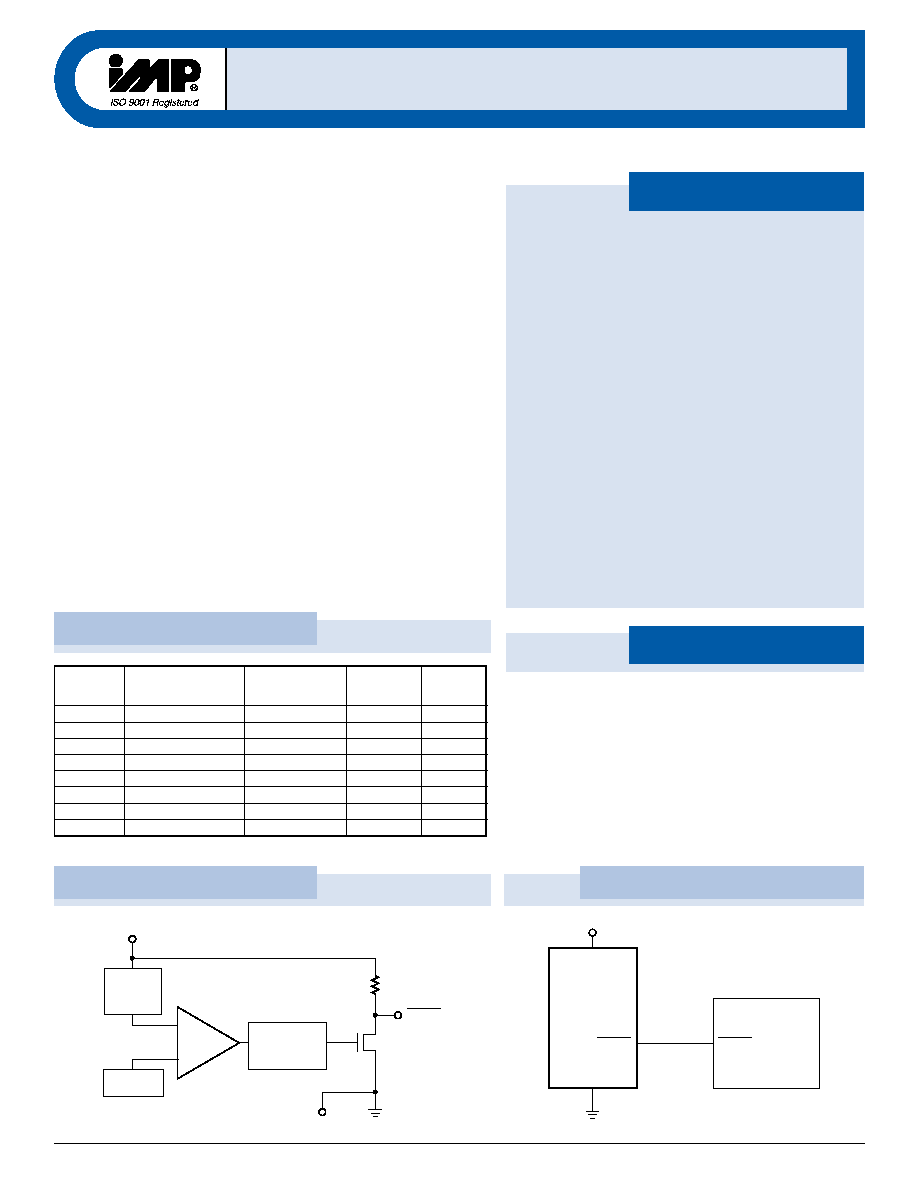

Block Diagram

≠

+

1233M_01.eps

V

CC

RESET

GND

5.0k

9

Supply

Tolerance

Bias

IMP1233M

Delay

350ms Typical

Reference

Lo

Lo

w P

w P

o

o

w

w

er

er

, 5V/3.0V

, 5V/3.0V

µ

µ

P R

P R

eset

eset

≠ A

≠ A

ctiv

ctiv

e L

e L

O

O

W

W

, Open-Dr

, Open-Dr

ain Output

ain Output

≠ 350ms R

≠ 350ms R

eset P

eset P

er

er

iod

iod

The IMP1233M supply voltage monitor is an improved, low-power

replacement for the Dallas Semiconductor DS1233M. Maximum supply

current over temperature is a low 20

µA, representing 60 percent lower

power as compared to the DS1233M.

The IMP1233M issues an active LOW reset signal whenever the moni-

tored supply is out-of-tolerance. A precision reference and comparator

circuit monitor power supply (V

CC

) level. Tolerance level options are

5- and 10-percent for a 5V power supply. The tolerance is 15-percent for

the 3.3V, IMP1233M. When an out-of-tolerance condition is detected, an

internal power-fail signal is generated which forces an active LOW reset

signal. After V

CC

returns to an in-tolerance condition, the reset signal

remains active for 350ms to allow the power supply and system micro-

processor to stabilize.

The IMP1233M is designed with a open-drain output stage and operates

over the extended industrial temperature range. Devices are available in

the compact surface mount SO-8 package.

Other low power products in this family include the IMP1810/11/12/15/

16/17 and IMP1233D.

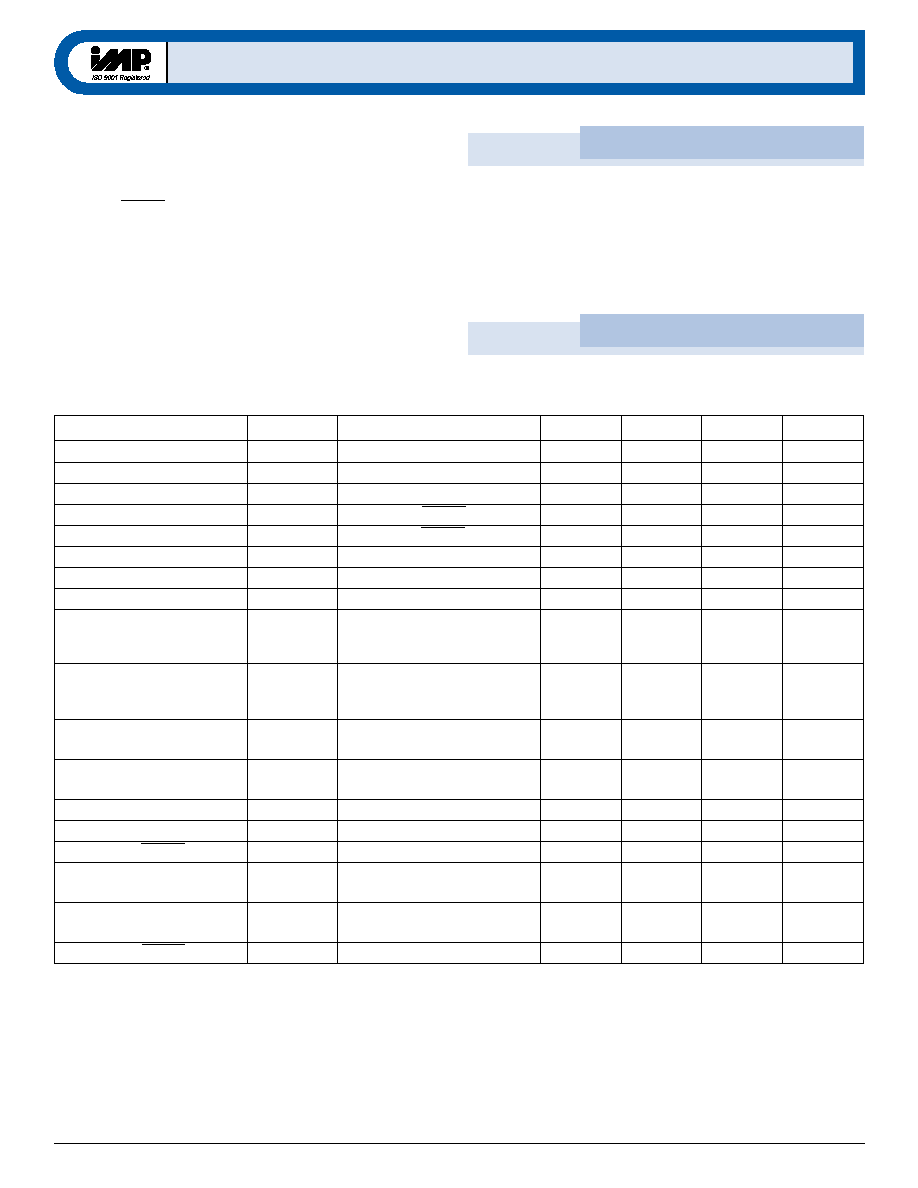

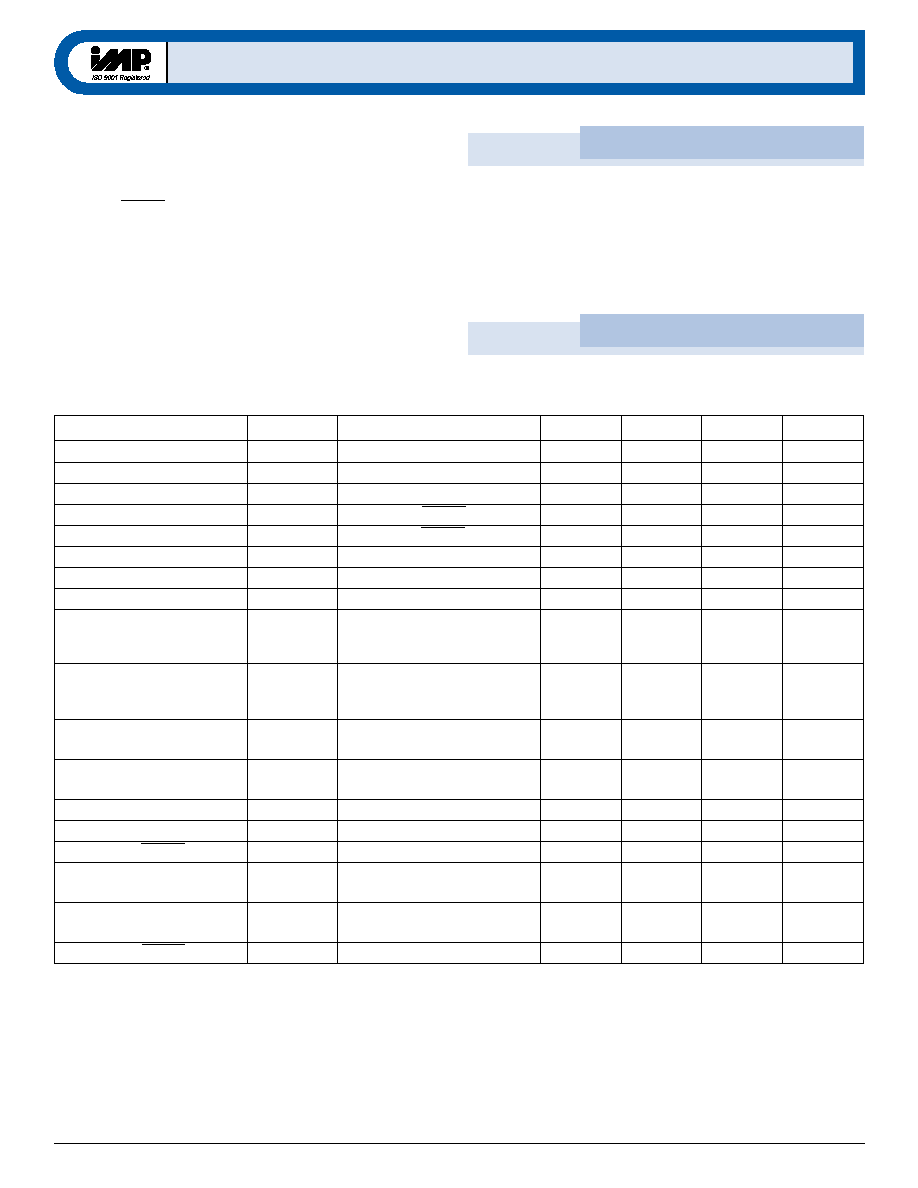

Typical Application

IMP1233M

Microprocessor

RESET

RESET

1233M_02.eps

VCC

GND

t

r

a

P

e

g

a

t

l

o

V

T

E

S

E

R

)

V

(

e

m

i

T

T

E

S

E

R

)

s

m

(

t

u

p

t

u

O

e

g

a

t

S

T

E

S

E

R

y

t

i

r

a

l

o

P

0

1

8

1

P

M

I

0

2

1

.

4

,

0

7

3

.

4

,

0

2

6

.

4

0

5

1

ll

u

P

-

h

s

u

P

W

O

L

1

1

8

1

P

M

I

0

3

1

.

4

,

0

5

3

.

4

,

0

2

6

.

4

0

5

1

n

i

a

r

D

-

n

e

p

O

W

O

L

2

1

8

1

P

M

I

0

3

1

.

4

,

0

5

3

.

4

,

0

2

6

.

4

0

5

1

ll

u

P

-

h

s

u

P

H

G

I

H

5

1

8

1

P

M

I

0

5

5

.

2

,

0

8

8

.

2

,

0

6

0

.

3

0

5

1

ll

u

P

-

h

s

u

P

W

O

L

6

1

8

1

P

M

I

0

5

5

.

2

,

0

8

8

.

2

,

0

6

0

.

3

0

5

1

n

i

a

r

D

-

n

e

p

O

W

O

L

7

1

8

1

P

M

I

0

5

5

.

2

,

0

8

8

.

2

,

0

6

0

.

3

0

5

1

ll

u

P

-

h

s

u

P

H

G

I

H

D

3

3

2

1

P

M

I

5

2

1

.

4

,

5

7

3

.

4

,

5

2

6

.

4

0

5

3

n

i

a

r

D

-

n

e

p

O

W

O

L

M

3

3

2

1

P

M

I

0

2

7

.

2

,

5

7

3

.

4

,

5

2

6

.

4

0

5

3

n

i

a

r

D

-

n

e

p

O

W

O

L

Family Selection Guide

I M P 1

I M P 1

2 3 3 M

2 3 3 M

2000 © IMP, Inc.

Microprocessor Supervisor

3

Notes: 1. A 1k

external resistor maybe required in some applications for proper operation of the microprocessor reset control circuit.

Absolute Maximum Ratings

Electrical Characteristics

Voltage on V

CC

. . . . . . . . . . . . . . . . . . . . . . . . ≠0.5V to 6.5V

Voltage on RESET . . . . . . . . . . . . . . . . . . . . . ≠0.5V to V

CC

+ 0.5V

Operating Temperature Range . . . . . . . . . . . ≠40

∞C to 85∞C

Soldering Temperature . . . . . . . . . . . . . . . . . . 260

∞C for 10 seconds

Storage Temperature . . . . . . . . . . . . . . . . . . . ≠55

∞C to 125∞C

Voltages measured with respect to ground.

These are stress ratings only and functional operation is not implied.

Parameter

Symbol

Conditions

Min

Typ

Max

Units

Supply Voltage

V

CC

1.2

5.5

V

Output Voltage

V

OH

I

OUT

< 500

µA

V

CC

≠ 0.5V

V

CC

≠ 0.1V

V

Output Current

I

OL

Output = 0.4V, V

CC

2.7V

+8

mA

Operating Current

I

CC

V

CC

< 5.5V, RESET output open

8

20

µA

Operating Current

I

CC

V

CC

3.6V, RESET output open

6

15

µA

V

CC

Trip Point (IMP1233M-5)

V

CCTP

4.25

4.375

4.49

V

V

CC

Trip Point (IMP1233M-55)

V

CCTP

4.5

4.625

4.75

V

V

CC

Trip Point (IMP1233M-3)

V

CCTP

2.64

2.72

2.8

V

Voltage High Trip Level

V

HTL

4.75

V

IMP1233M-5

IMP1233M-55

Voltage Low Trip Level

V

LTL

4.00

V

IMP1233M-5

IMP1233M-55

Voltage High Trip Level

V

HTL

3.14

V

IMP1233M-3

Voltage Low Trip Level

V

LTL

2.48

V

IMP1233M-3

Internal Pull-Up Resistor

R

P

3.5

5.0

7.5

k

Output Capacitance

C

OUT

10

pF

V

CC

Detect to RESET Low

t

RPD

2

10

µs

V

CC

Slew Rate

t

F

300

µs

(V

HTL

- V

LTL

)

V

CC

Slew Rate

t

R

0

ns

(V

LTL

- V

HTL

)

V

CC

Detect to RESET High

t

RPU

t

R

= 5

µs

200

350

500

ms

Unless otherwise noted, V

CC

= 1.2V to 5.5V and specifications are over the operating temperature range of ≠ 40

∞C to +85∞C.

All voltages are referenced to ground.

I M P 1

I M P 1

2 3 3 M

2 3 3 M

4

408-432-9100/www.impweb.com

2000 © IMP, Inc.

!

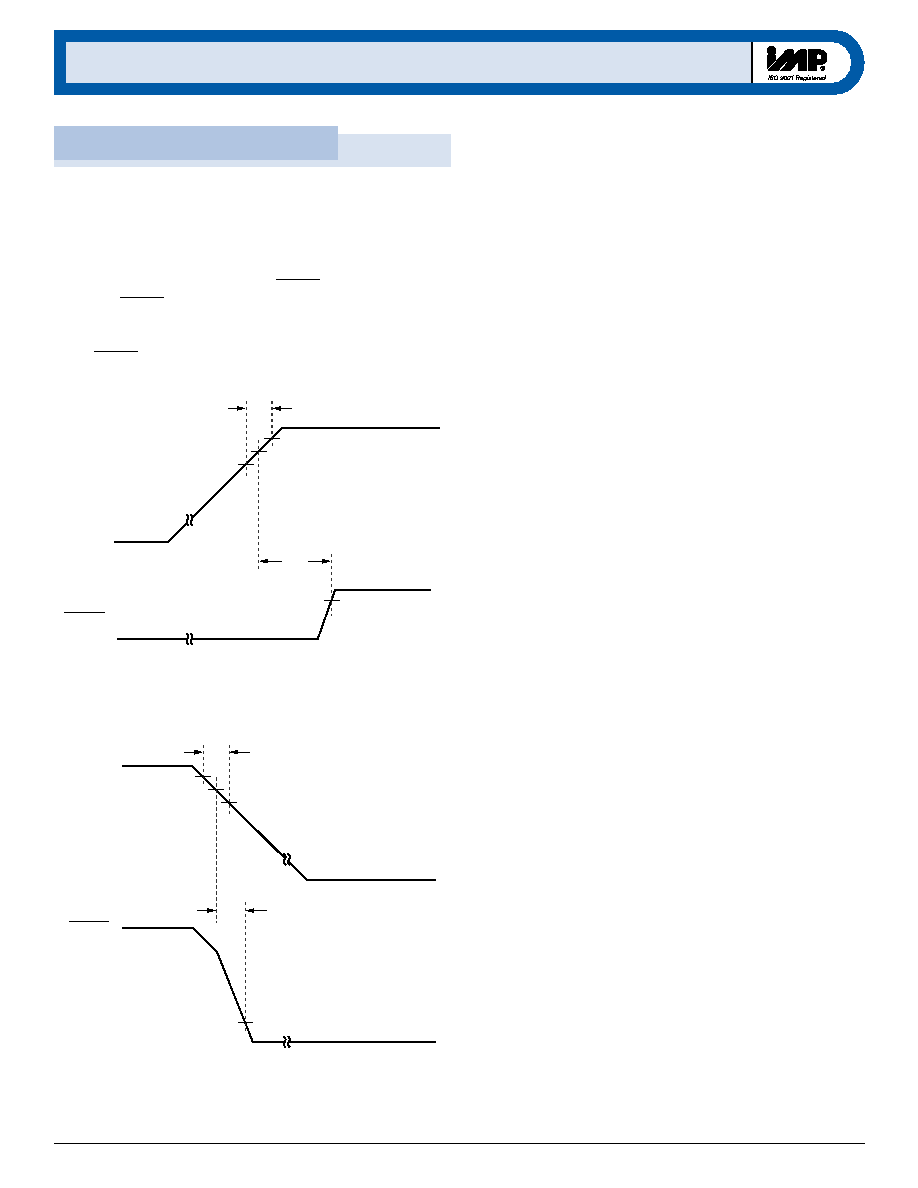

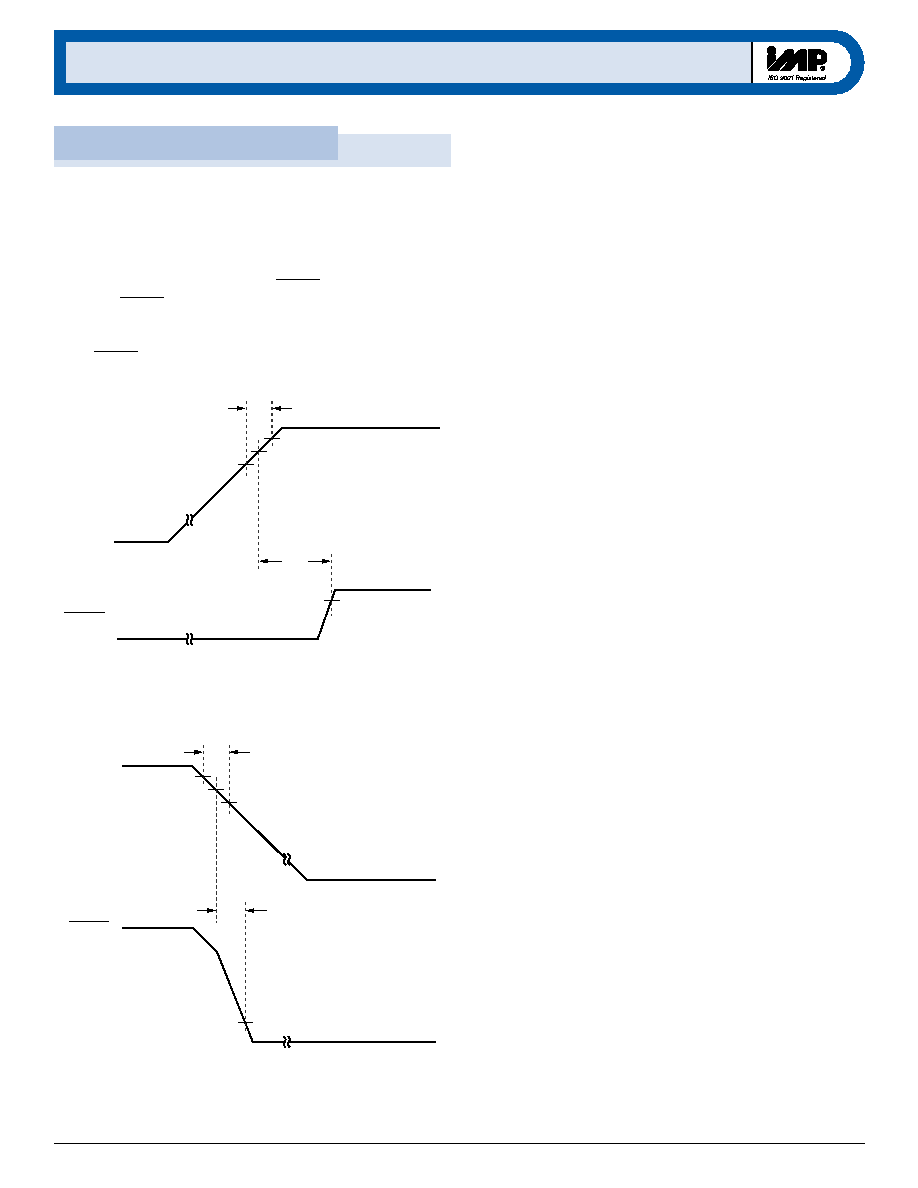

Operation ≠ Power Monitor

The IMP1233M detects out-of-tolerance power supply conditions.

It resets a processor during power-up and issues a reset to the

system processor when the monitored power supply voltage

is below the reset threshold (power-down). When an out-of-

tolerance V

CC

voltage is detected, the RESET signal is asserted. On

power-up, RESET is kept active (LOW) for approximately 350ms

after the power supply voltage has reached the selected tolerance.

This allows the power supply and microprocessor to stabilize

before RESET is released.

Figure 1. Timing Diagram: Power-Up

Figure 2. Timing Diagram: Power-Down

V

HTL

V

CCTP

V

LTL

V

CC

RESET

t

R

t

RPU

V

OH

1233M_05.eps

V

HTL

V

CCTP

V

LTL

V

CC

RESET

t

F

V

OL

t

RPD

1233M_06.eps

Application Information